# 3-channel LED display driver

## UCS1903N

## GENERAL DESCRIPTION

The UCS1903N is a 3-channel LED display driver / controller with a built-in MCU digital interface, data latches and LED high voltage driving functions. It features superior performances and reliable functions. Under the control of the external MCU, it performs independent grayscale control through data-cascading transfer for driving large outdoor colour dot-matrix LED panels.

## FEATURES

- 1. single line data tronsmission (return to zero code)

- 2. shaping transmit specific technology, Cascade number of lamps and lanterns is not restricted

- 3. cascading ability enhancement technology, Any 2 lanterns spacing can be up to 10 meters

- 4. Data transfer rate of 800 k/s, Images of not less than 1024 points can be realized when the refresh rate of 30 frames per second,

- 5. RGB output port PWM control can be achieved 256 grey level adjustment, port scanning frequency of 1.5 KHz/s

- 6. chip VDD built-in 5 v voltage regulator tube, output port Withstand Voltage is greater than 24 V

- adopt the preset 17 mA/channel constant current mode. High precision of constant current, differences of current between Channel is less than ±1.5%, the differences of current between Chip is less than ±3%

- 8. when power up ,IC self-inspection then Light connection on the pin B lamp

- 9. SA-I Anti-interference patent technology for single line data tronsmission

- 10. Industrial design, stable and reliable

## Application:

Point light source full color module full color light bar LED decorate..

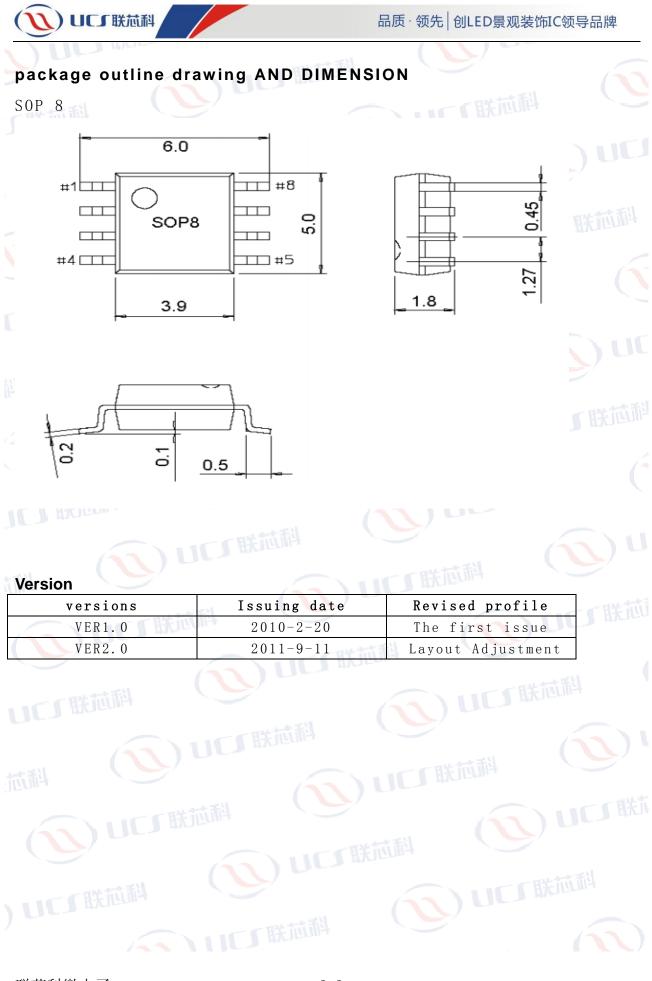

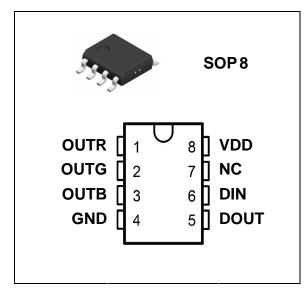

## **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| Number | Symbol | Name             | Function Description         |

|--------|--------|------------------|------------------------------|

| 1      | OUTR   | LED drive output | Red PWM control output       |

| 2      | OUTG   | LED drive output | Green PWM control output     |

| 3      | OUTB   | LED drive output | Blue PWM control output      |

| 4      | GND    | Ground           | Ground                       |

| 5      | DOUT   | Data output      | Display data cascaded output |

| 6      | DIN    | Data input       | Display data cascaded input  |

| 7      | NC     |                  |                              |

| 8      | VDD    |                  | Logic power supply           |

品质·领先 创LED景观装饰IC领导品牌

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> =25 °C, V <sub>SS</sub> =0 V, unless othe | wise specified) |

|------------------------------------------------------------------------------------|-----------------|

|------------------------------------------------------------------------------------|-----------------|

UCJ联芯科

| Parameter                      | Symbol           | Value                    | Unit |

|--------------------------------|------------------|--------------------------|------|

| Logic supply voltage           | V <sub>DD</sub>  | +7.0                     | V    |

| Output port limitation voltage | V <sub>OUT</sub> | 28                       | V    |

| Logic input voltage            | V                | $-0.5$ to $V_{DD}$ + 0.5 | V    |

| Operating temperature          | T <sub>OPT</sub> | -40 to +85               | °C   |

| Storage temperature            | T <sub>STG</sub> | -55 to +150              | °C   |

| antistatic                     | ESD              | 6000                     | V    |

| output rating                  | Pd               | 400                      | mW   |

**RECOMMENDED OPERATNG RANGES** ( $T_A = -20$  to  $+70 \degree$ C,  $V_{SS} = 0 V$ , unless otherwise specified)

| Parameter                 | Symbol          | Min.                | Тур. | Max                 | Unit |

|---------------------------|-----------------|---------------------|------|---------------------|------|

| Logic supply voltage      | V <sub>DD</sub> | -                   | 5.5  |                     | V    |

| High level input voltage  | V <sub>IH</sub> | 0.7 V <sub>DD</sub> | -    | V <sub>DD</sub>     | V    |

| Low level input voltage 💊 | V <sub>IL</sub> | 0                   | Sin  | 0.3 V <sub>DD</sub> | V    |

| Output port rated voltage | Vout            | 24                  |      |                     | V    |

# **ELECTRICAL CHARACTERISTICS** ( $T_A = -20$ to +70 °C, $V_{DD} = 4.5$ to 5.5 V, $V_{SS} = 0$ V, unless otherwise specified)

| Parameter                   | Symbol   | Min.   | Тур.          | Max                    | Unit         | Test conditions     |

|-----------------------------|----------|--------|---------------|------------------------|--------------|---------------------|

| Low level output current    | lout     | 16.5   | 17            | 17.5                   | mA           | R, G, B             |

| Low level output<br>current | Ido      | 10     | -             | $\overline{()}$        | mA           | Vo = 0.4 V,<br>Dout |

| High level input voltage    | Vih      | 0.6Vdd | - L           |                        | V            |                     |

| Low level input voltage     | Vil      | -      | -             | 0.3 Vdd                | V            |                     |

| Voltage hysteresis          | Vh       | - 6    | 0.35          | CT IN                  | V            |                     |

| quiescent current           | IDDdyn   |        | $\mathcal{T}$ | 1                      | mA           | 无负载                 |

| rated power                 | PD       |        | - Rtini       | 250                    | mW           | (Ta=25℃)            |

| thermal resistance          | Rth(j-a) | U C    | 80            | 190                    | °C <b>/W</b> | and the             |

| してよ既証料                      |          |        |               | $\widehat{\mathbf{n}}$ | ) UC         | THE DECKING         |

联芯科(深圳)微电子地址:深圳市福田区车公庙安华工业区6栋301电话: 0755-25866271传真: 0755-25866242www.szucs.cn

**SWITCHING CHARACTERISTICS** ( $T_A = -20$  to +70 °C,  $V_{DD} = 4.5$  to 5.5 V,  $V_{SS} = 0$  V, unless otherwise specified)

| Parameter              | Symbol           | Min.  | Тур.       | Max | Unit | Test conditions                                                                              |

|------------------------|------------------|-------|------------|-----|------|----------------------------------------------------------------------------------------------|

| Propagation delay time | t <sub>PLZ</sub> | 01121 | -          | 300 | ns   | $C_L = 15 \mathrm{pF},  \mathrm{DIN} \rightarrow \mathrm{DOUT}, \ R_L = 10 \mathrm{k\Omega}$ |

| Fall time              | t <sub>THZ</sub> |       | <u>)</u> U | 120 | μs   | $C_L = 300  \text{pF},$<br>OUTR/OUTG/OUTB                                                    |

| Data transfer rate     | F <sub>MAX</sub> | 800   | -          |     | kbps | 50 % duty cycle                                                                              |

| Input capacitance      | C                | 151   | 一時间        | 15  | pF   | <u> </u>                                                                                     |

## FUNCTIONAL DESCRIPTION

UCJ联芯科

The UCS1903N sends signals in return to zero codes with a single-wire communication method. When the power-on reset is completed, the UCS1903N receives the data from the DIN pin. When all the 24 bits of data have been received, IC no longer receive data , the DOUT port starts to forward the data to the next chip as its input data. The DOUT pin is held LOW before the data forwarding,. The three PWM output ports, OUTR, OUTG and OUTB, drive Duty ratio output in a 0.6-ms period corresponding to the 24-bit data received before. If the input data from the DIN pin is a RESET code , the UCS1903N will drive the newest received 24-bit data for display. When the reset code is completed, the UCS1903N will start receive the new 24-bit data. When 24 bits of data have been received, the output at the OUTR, OUTG and OUTB pins will remain unchanged. When a low level RESET code longer than 24µs is received, the UCS1903N will drive Duty ratio output corresponding to the newest 24-bit data received.

The UCS1903N employs an automatic shaping-forwarding technique, so the number of the cascaded chips is not limited by the signal transfer, and is only limited by the panel refresh speed. For example, in a 1024-chip cascaded design with the panel refresh time of 1024X3X8 X 1.25 (us) =30ms), no flickering will appear.

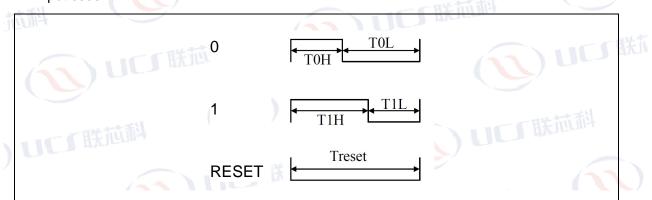

## **TIMING WAVEFORMS**

1 Input code

| Name  | Description                | Typ. value | error                 |

|-------|----------------------------|------------|-----------------------|

| ТОН   | 0 code, up level time      | 0. 4µs     | $\pm 40  \mathrm{ns}$ |

| T1H   | 1 code, up level time      | 0.8µs      | ±80ns                 |

| TOL   | 0 code, Low level time     | 0.8µs      | $\pm 80$ ns           |

| T1L   | 1 code, low level time     | 0. 4µs     | $\pm 40\mathrm{ns}$   |

| Reset | Reset code, Low level time | >24us      |                       |

| Name  | Description                | Typ. value |                |

|-------|----------------------------|------------|----------------|

| ТОН   | O code, up level time      | 0.4µs      | $(\mathbf{n})$ |

| Т1Н   | 1 code, up level time      | 0.8µs      | <b>S</b>       |

| TOL   | 0 code, Low level time     | 0.9µs      | - 114 1        |

| T1L   | 1 code, low level time     | 0.5µs      | ) UCJ HAN      |

| Reset | Reset code, Low level time | >24us      |                |

Connection scheme 4

D1 D3 D2 D4 DIN DO DIN DO DIN DO ► Chip 3 Chip 1 Chip 2 してよ熊河村

| Data tr | ansfer form | at                     |             |               |             |                       | 1           |               |          |

|---------|-------------|------------------------|-------------|---------------|-------------|-----------------------|-------------|---------------|----------|

|         |             | 5                      |             | ≥24µ:<br>∣    | s<br>I      | $\mathbf{C}$          |             |               | 6        |

|         | k           | Data refres<br>cycle 1 | h           | $\mapsto$     | ₹           | Data refre<br>cycle 2 |             | $\rightarrow$ |          |

| D1_     | 1st 24 bits | 2nd 24 bits            | 3rd 24 bits | RESET<br>CODE | 1st 24 bits | 2nd 24 bits           | 3rd 24 bits | RESET         |          |

| D2_     |             | 2nd 24 bits            | 3rd 24 bits | RESET<br>CODE |             | 2nd 24 bits           | 3rd 24 bits | RESET<br>CODE | + tri fi |

| D3_     |             |                        | 3rd 24 bits | RESET<br>CODE |             |                       | 3rd 24 bits | RESET         | 7Jeur    |

| D4_     |             |                        |             |               |             |                       |             |               |          |

|         |             |                        |             |               |             |                       |             |               |          |

**Note:** D1 is the data sented from the MCU, D2, D3 and D4 are the data automatically shaped and forwarded by the cascaded circuit.

## 6. 24-bit data format

| ~ | R7 | R6 | R5  | R4    | R3 | R2 | R1 | R0 | G7 | G6 | G5 | G4 | G3 | G2 | G1 | G0 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | В0 |

|---|----|----|-----|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| l |    |    | 100 | His I |    |    |    |    | 1  |    |    |    |    |    |    | 1  |    | -  |    |    |    |    |    |    |

Note: The data is sent in the sequence of RGB, and the MSB is sent first.

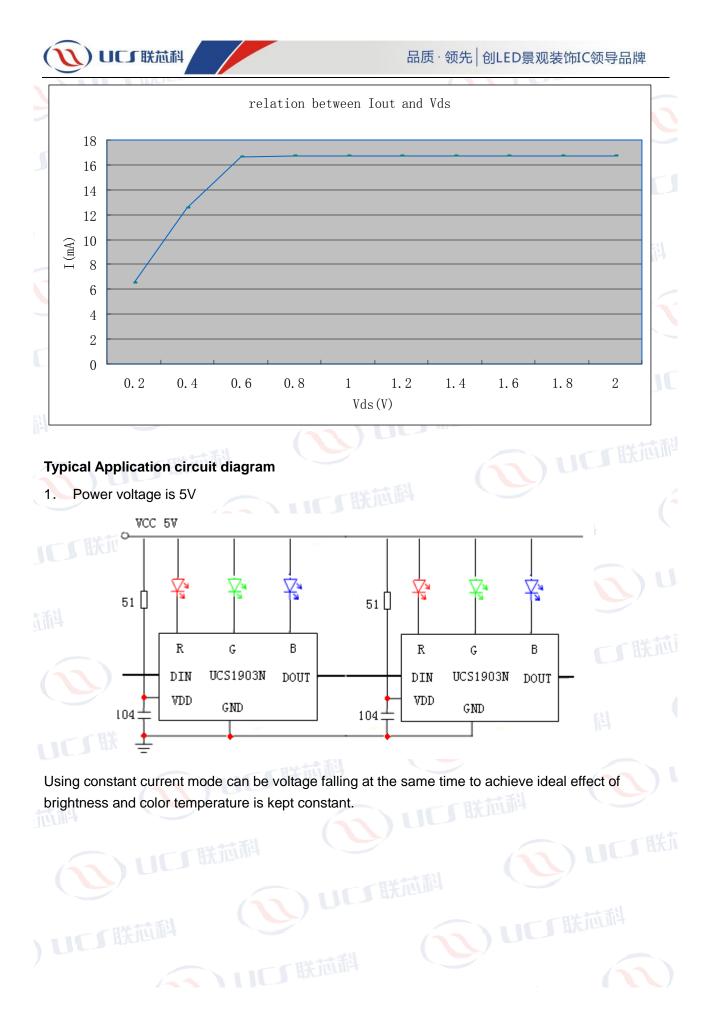

### constant current characteristic

i i i i i

UCS1903N Constant current characteristic is excellent, between Channel, even between chip, the differences of current is tiny

(1): the differences of current between Channel is less than  $\pm 1.5\%$ . the differences of current between Chip is less than  $\pm 3\%$

(2): When the voltage of the load change, UCS1903N output current is not affected, as shown in the figure below

(3): Below UCS1903N output port of the current lout and add on the port voltage Vds curve relationship。 the smaller the lout current, the smaller in the condition of constant current need of Vds.

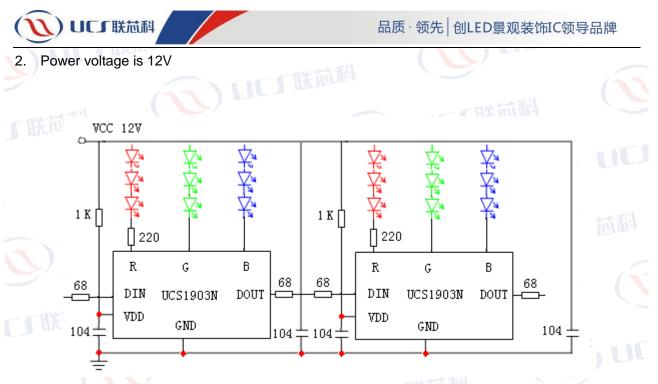

In order to prevent the damage of charged pull plug, when 12 v power supply, Din and Do all the string in a 68-80 ohm resistor for protection

In order to reduce the interference, between each lamps and lanterns of power supply and ground multiple a capacitance of 104 or 105

3. Power voltage is 24V VCC24V Ó з к 🗍 З К 🗍 Πr R R G В R G В 120 120 120 120 DIN DOUT DIN UCS1903N DOUT UCS1903N VDD VDD GND GND 104  $104 \pm$ 104 =104

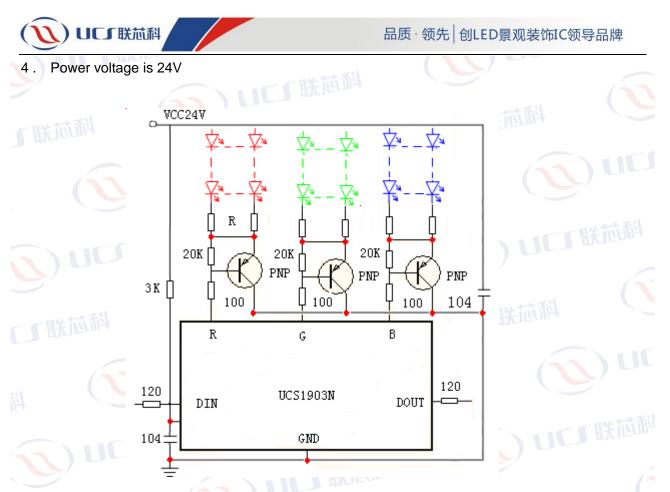

In order to prevent the damage of charged pull plug, when 24 v power supply, Din and Do all the string in a 120 ohm resistor for protection In order to reduce the interference, between each lamps and lanterns of power supply and ground multiple a capacitance of 104 or 105

Attention : Shown above for the PNP transistor, 9012,8550 is work In order to prevent the damage of charged pull plug, when 24 v power supply, Din and Do all the string in a 120 ohm resistor for protection

In order to reduce the interference, between each lamps and lanterns of power supply and ground multiple a capacitance of 104 or 105

in.

## Vds Definition and values

Vds is the output voltage on the RGB pin. In order to avoid more than PD, Vds is no more than 4.5 v .The following formula is Vds:

Vds=VCC-I\*R-N\*Vled

Attention: I is Each string on the LED current, R is the resistance of LED series, N is the LED series connection number, Vled is the LED voltage

## stabilizing voltage characteristic

UCS1903N built-in stabilizer, according to the power supply voltage (VCC) is different, must choose different resistance (R) for step-down voltage, Resistance to select in the table below for reference:

| VCC (V)    | R(ohm)    |

|------------|-----------|

| 5          | 51-80     |

| 12         | 750-1K    |

| 15         | 1.2K-1.5K |

| <b>2</b> 4 | 2.4K- 3K  |